3D Modeling of Microelectronic Structures with EDAMAME™

We developed a lightweight modeling tool called EDAMAME™ (EDA Modeling and Meshing Environment) that builds 3D models of microelectronic structures based on emulation of etch and deposition processes. The tool takes GDS-II artwork and a description of the process steps as input, and produces source files for 3rd-party mesh tools and field solvers as well as the FASTCAP capacitance extraction tool, allowing us to model capacitance, electrostatic potential and fields, heat flow, and other effects.

Targets for modeling include floating-gate structures (e.g., in CCD amplifiers and non-volatile memory elements), MEMS devices, CMOS structures and interconnects, and many other structures produced by microelectronic fabrication methods.

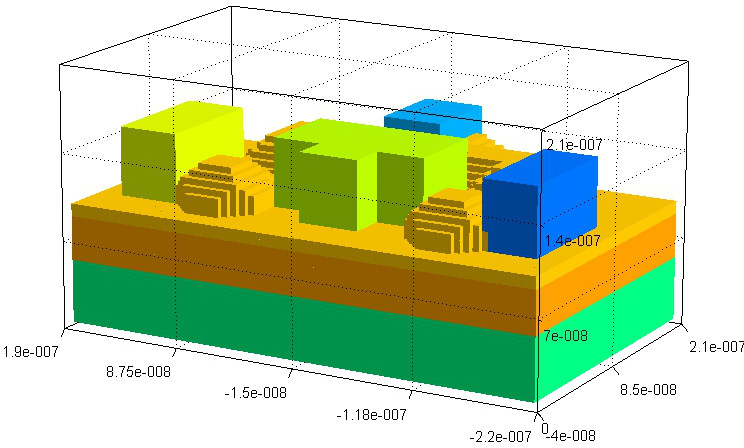

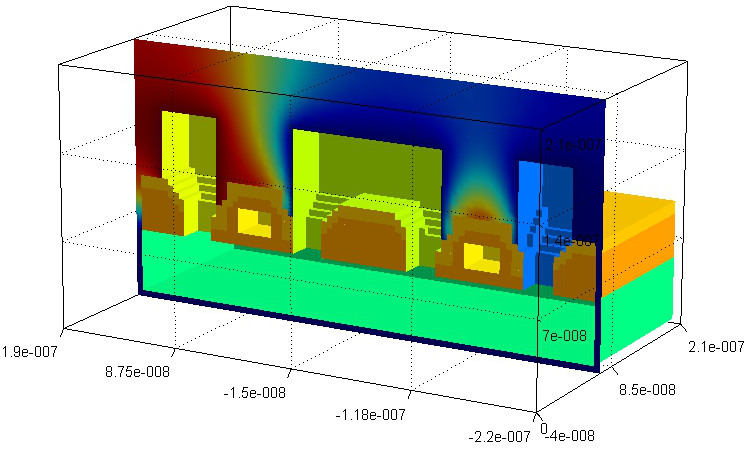

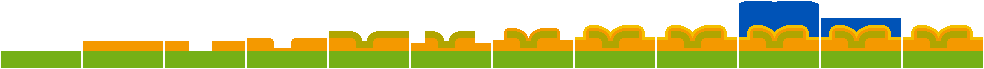

Here we show the potential profile in a cross-section of a CMOS inverter. The structure was built up in a series of deposition and etch steps shown above and below along orthogonal cross sections through the center of the structure. The resulting 3D model and its potential profile along one cross section are shown at right.

Over the past two decades the SST team and its licensing partners developed three generations of SuperFlash split-gate technology, down to 55/45 nm as of today, and the technology has become a popular choice for embedded SoC designs and the MCU market. As we continue to scale flash cell technology, the importance of understanding 3D effects on a cell's active and parasitic capacitances is hard to overestimate. In 2013 we reviewed a number of potential collaborators for a 3D Flash capacitance modeling project before choosing the VivEng team. We received and validated a completely integrated 3D CAP simulation tool ahead of schedule and meeting all our expectations. It works on a laptop system and provides excellent accuracy in less than an hour for most of our cases. It is a great tool which helps our engineers to quickly evaluate new cell structure ideas, run cell layout & process optimization, and what is most important - save technology scaling and development project costs and time.

-- Alex Kotov, Fellow, SST-Microchip